# MODELLING AND OPTIMIZATION OF SUBTHRESHOLD LEAKAGE CURRENT IN LOW-POWER, SILICON-BASED, COMPLEMENTARY METAL OXIDE SEMICONDUCTOR (CMOS) DEVICES

# BY KUSIMBA STEPHEN

A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN PHYSICS TO THE DEPARTMENT OF PHYSICS, SCHOOL OF SCIENCE, UNIVERSITY OF ELDORET, KENYA

Date .....

#### **DECLARATION**

### **Declaration by the Student**

| This thesis is my original work and has not been presented for a degree in any other |                             |  |

|--------------------------------------------------------------------------------------|-----------------------------|--|

| University. No part of this thesis may be reproduce                                  | d without the prior written |  |

| permission of the author and/ or University of Eldoret, Kenya.                       |                             |  |

|                                                                                      |                             |  |

| Kusimba Stephen                                                                      | Date                        |  |

| SC/PGP/005/09                                                                        |                             |  |

|                                                                                      |                             |  |

| Approval by the Supervisors                                                          |                             |  |

| This thesis has been submitted for examination with                                  | our approval as University  |  |

| supervisors.                                                                         |                             |  |

|                                                                                      |                             |  |

| Professor Samuel K. Rotich                                                           | Date                        |  |

| Department of Mathematics and Physics                                                |                             |  |

| Moi University, Kenya                                                                |                             |  |

Department of Physics

University of Eldoret, Kenya

Professor J.K. Tonui

## **DEDICATION**

I would like to thank my family to which I dedicate this work.

#### **ABSTRACT**

The trend of process scaling for CMOS technology has made subthreshold leakage reduction a growing concern for submicron circuit designers. Power consumption has become a principle design consideration as device sizes decrease and many more devices fit on a single chip. Since switching power is proportional to the square of the supply voltage, V 2<sub>dd</sub>, new processes are tailored for lower supply voltages. The decrease in V<sub>dd</sub> slows down devices, which requires that the threshold voltage, V<sub>th</sub>, must be lowered to maintain performance. This reduction of V<sub>th</sub> produces the exponential increase of subthreshold leakage currents. This research demonstrates a process used to model and optimize subthreshold leakage current for a CMOS device during its standby mode (OFF-state). The process involves the use of MATHCAD to examine the OFF-state subthreshold leakage current, I<sub>sub</sub> (OFF), based on variations in the threshold voltage, V<sub>th</sub>, the effective transistor channel length, L, and the effective transistor channel width, W. The theoretical work entails simplifying the empirical relationship between the surface inversion potential,  $\varphi_s$ , the gate-source voltage, V<sub>gs</sub>, and the Subthreshold swing coefficient, n. This results in an expression relating the OFF-state subthreshold leakage current, I<sub>sub</sub> (OFF), the threshold voltage, V<sub>th</sub>, the effective transistor channel length, L, and the effective transistor channel width, W. Analyzing the resulting equation using MATHCAD confirms that the OFF-state subthreshold leakage current, I<sub>sub</sub> (OFF) increases exponentially with a decrease in the threshold voltage, V<sub>th</sub>, and linearly with a decrease in the effective transistor channel length, L. The results also show that the OFF-state subthreshold leakage current, I<sub>sub</sub> (OFF), increases linearly with the effective transistor channel width, W. The optimization process resulted in the values of  $V_{th} = 140 \text{ mV}$ , L = 28 nm and W = 7 nm which give the desired outcome of greatly reduced OFF-state subthreshold leakage current,  $I_{sub}$  (OFF) = 0.125 nA, for a single transistor. Field Programmable Gate Arrays (FPGAs) are one type of chip that could benefit from such subthreshold leakage reduction techniques.

#### TABLE OF CONTENTS

| DECLARATION                                            | i    |

|--------------------------------------------------------|------|

| DEDICATION                                             | ii   |

| ABSTRACT                                               | iii  |

| TABLE OF CONTENTS                                      | iv   |

| LIST OF TABLES                                         | vii  |

| LIST OF FIGURES                                        | viii |

| ABBREVIATIONS, ACRONYMS AND SYMBOLS                    | ix   |

| ACKNOWLEDGEMENT                                        | xiii |

| CHAPTER ONE                                            | 1    |

| INTRODUCTION                                           | 1    |

| 1.1 Background                                         | 1    |

| 1.2 Problem Statement                                  | 2    |

| 1.3 Objectives:                                        | 3    |

| 1.3.1 General Objective                                | 3    |

| 1.3.2 Specific Objectives                              | 3    |

| 1.4 Justification                                      | 4    |

| CHAPTER TWO                                            | 6    |

| THEORY AND LITERATURE REVIEW                           | 6    |

| 2.1 Introduction                                       | 6    |

| 2.2 The MOSFET Fundamentals                            | 6    |

| 2.3 The CMOS Transistor                                | 9    |

| 2.4 Leakage current mechanisms in scaled CMOS devices: | 12   |

|                 | 2.4.1 Gate Oxide Tunneling Current                                                                                                                                                                                    |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2               | 2.4.2 Band-To-Band Tunneling (BTBT) Current                                                                                                                                                                           |  |

| 2               | 2.4.3 Punchthrough Current                                                                                                                                                                                            |  |

| 2               | 2.4.4 Subthreshold Leakage Current                                                                                                                                                                                    |  |

| 2               | 2.5 Subthreshold Leakage Current Models:                                                                                                                                                                              |  |

| 2               | 2.6 Some Existing Techniques for Subthreshold Leakage Current reduction:                                                                                                                                              |  |

| 2               | 2.6.1 Switched Source Impedance 27                                                                                                                                                                                    |  |

| 2               | 2.6.2 Stack Effect                                                                                                                                                                                                    |  |

| 2               | 2.6.3 Body Biasing                                                                                                                                                                                                    |  |

| 2               | 2.6.4 Dual-Threshold CMOS30                                                                                                                                                                                           |  |

| 2               | 2.6.5 Multi-Threshold CMOS (MTCMOS)                                                                                                                                                                                   |  |

| 2               | 2.6.6 Boosted Gate MOS (BGMOS) and Super Cut-Off CMOS (SCCMOS)32                                                                                                                                                      |  |

| CII             |                                                                                                                                                                                                                       |  |

| CH.             | APTER THREE34                                                                                                                                                                                                         |  |

|                 | APTER THREE                                                                                                                                                                                                           |  |

| ME              |                                                                                                                                                                                                                       |  |

| ME              | THODOLOGY34                                                                                                                                                                                                           |  |

| ME              | THODOLOGY                                                                                                                                                                                                             |  |

| ME              | 34 3.1 Introduction                                                                                                                                                                                                   |  |

| ME<br>CH<br>RES | THODOLOGY                                                                                                                                                                                                             |  |

| ME  CH  RES     | THODOLOGY                                                                                                                                                                                                             |  |

| ME  CH  RES     | 2THODOLOGY       34         3.1 Introduction       34         3.2 Derivation of the simulation equation       34         APTER FOUR       38         SULTS AND DISCUSSIONS       38         4.1 Introduction       38 |  |

| ME CH RES       | 34 3.1 Introduction                                                                                                                                                                                                   |  |

| CHAPTER FIVE                   | 50 |

|--------------------------------|----|

| CONCLUSION AND RECOMMENDATIONS | 50 |

| 5.1 Conclusion                 | 50 |

| 5.2 Recommendations            | 51 |

| REFERENCES                     | 52 |

| APPENDIX                       | 59 |

#### LIST OF TABLES

| Table A1: Variation of I <sub>sub</sub> (L) and Channel length L                                  | 61 |

|---------------------------------------------------------------------------------------------------|----|

| Table A 2: Variation of I <sub>sub</sub> (W) and Channel width W                                  | 62 |

| Table A 3: Variation of I <sub>sub</sub> (V <sub>th</sub> ) and Threshold voltage V <sub>th</sub> | 63 |

#### LIST OF FIGURES

| Figure 2.1: Important MOSFET parameters (NMOS) (Butzen, et.al., 2007)               | 7  |

|-------------------------------------------------------------------------------------|----|

| Figure 2.2: Schematic diagrams of a CMOS inverter (Taur, et.al., 1998, Sze, et.al., |    |

| 2007)                                                                               | 0  |

| Figure 2.3: Major leakage mechanisms in MOS transistors (Butzen, et.al., 2007) 1    | 2  |

| Figure 2. 4: Three mechanisms of gate dielectric tunneling leakage (Cao, 2000) 1    | 3  |

| Figure 2.5: BTBT in reverse-biased p-n junction (Vijayalakshmi, 2017) 1             | 5  |

| Figure 2.6: I-V characteristics of a 65 nm nMOS transistor at 70°C on a log scale   |    |

| (Weste, et.al., 2016)                                                               | 23 |

| Figure 2.7: Switched-Source-Impedance, (a) Circuit Example, (b) Savings             |    |

| (Horiguchi, et.al., 1993)                                                           | 27 |

| Figure 2.8: Artificial Creation of Stack Effect (Saxena, et.al., 2013)              | 28 |

| Figure 2.9: MTCMOS Schematic (Kumar, et.al., 2013)                                  | 1  |

| Figure 4.1: Variation of I <sub>sub</sub> with V <sub>th</sub>                      | -0 |

| Figure 4.2: Variation of Isub with W                                                | 3  |

| Figure 4.3: Variation of Isub with L                                                | -6 |

| Figure A 1: Drain Induced Barrier Lowering (DIBL) for low L                         | 50 |

#### ABBREVIATIONS, ACRONYMS AND SYMBOLS

C<sub>L</sub>: Load Capacitance

$V_{dd}$ : Supply Voltage

A: Ampere

b: Bulk or Substrate

BGMOS: Boosted Gate CMOS

BSIM MOS: Berkeley Short-Channel IGFET Model for MOS transistors

BTBT: Band-To-Band Tunneling

C<sub>b</sub>: Bulk (Substrate) capacitance

C<sub>dep</sub>: Capacitance of the depletion layer

C<sub>g</sub>: Gate capacitance

CMOS: Complementary Metal Oxide Semiconductor

C<sub>ox</sub>: Gate oxide capacitance

CPU: Central Processing Unit

d: Drain

DIBL: Drain Induced Barrier Lowering

E: Electric field

ECB: Electron Conduction-Band

eV: electronvolt

EVB: Electron Valence-Band

FET: Field Effect Transistor

FPGAs: Field Programmable Gate Arrays

g: Gate

GIDL: Gate Induced Drain Leakage

GND: Ground (Earth)

h: Planck's constant

$\frac{1}{2\pi}$  times the Planck's constant.

HVB: Hole-Valence-Band

IC: Integrated Circuit

$I_{d(weak)}$ : Drain current in the weak or subthreshold regime

IEEE: Institute of Electrical and Electronics Engineering

IGFET: Insulated Gate Field Effect Transistor

I<sub>sub</sub> or I<sub>sub</sub>(OFF): Subthreshold Leakage Current

J: Current density

J<sub>ECB</sub>: Electron-Conduction band Tunneling current density

J<sub>EVB</sub>: Electron-Valence band Tunneling current density

J<sub>HVB</sub>: Hole-Valence band Tunneling current density

k: Boltzmann's constant;  $1.38 \times 10^{-23}$  J/mol. K

K: Body effect model parameter

L: Transistor effective Channel length

MATHCAD: Modelling software

MOS: Short for MOSFET

MOSFET: Metal Oxide Semiconductor Field Effect Transistor

MTCMOS: Multi Threshold CMOS

η: Drain Induced Barrier Lowering (DIBL) Coefficient

NAND: Not AND logic gate

N<sub>CH</sub>: n-channel

NMOS: n-channel MOSFET

PMOS: p-channel MOSFET

q: Electronic Charge

S: Subthreshold swing

s: Source

SCCMOS: Super Cut-off CMOS

SCE: Short Channel Effect

SiO<sub>2</sub>: Silicon dioxide

SOI: Silicon-on-Insulator

t<sub>ox</sub>: Gate oxide thickness

VBBT: Variable Body Biasing Technique

V<sub>bs</sub>: Body bias voltage

V<sub>ds</sub>: Drain-to-Source voltage

V<sub>fb</sub>: Flat band voltage

V<sub>gs</sub>: Gate-to-Source voltage

VLSI: Very Large Scale Integration

$V_{ox}$ : Voltage drop across the oxide

V<sub>T</sub>: Thermal voltage

V<sub>th</sub>: Threshold voltage

V<sub>tho</sub>: Zero-bias voltage

W: Transistor effective Channel width

γ: Linearized body effect coefficient

φ: Surface to drain barrier height

$\phi_{ox}$ : Oxide tunneling barrier height

$\phi_s$ : Surface-inversion potential

$\omega_d$ : Depletion width under the channel

$\mathcal{E}_{ox}$ : Dielectric constant of Oxide

$\mathcal{E}_{si}$ : Dielectric constant of Silicon

$\mu_0$ : Carrier mobility

#### **ACKNOWLEDGEMENT**

First, I would like to thank God for my wonderful life. I would like to express my sincere gratitude to my supervisors; Professor S.K. Rotich and Professor J.K. Tonui for the constant and unconditional support they offered during my research.

Thank you Brenda, Adrian, G. Neville, Clive, Blessing and Kimberly for being my side with love and support since you came into my life. Your support, encouragement and patience are a sacrifice beyond measure. Thank you my parents, brothers and sisters for the strength you always wished me during my undergraduate and graduate studies.

Finally, I would like to thank my classmates from University of Eldoret for the good friendship and the excellent working environment. Thank you my friends for giving me assistance to let me through the difficulties and making my life so happy and fulfilled of emotion.

#### **CHAPTER ONE**

#### INTRODUCTION

#### 1.1 Background

The increasing prominence of portable systems and the need to limit power consumption in Very Large Scale Integration (VLSI) chips has led to rapid and innovative developments of low power devices in recent years. The increasing need of mobile communication represented by the mobile telephone has been showing remarkable growth. This market has been making tough demands for semiconductor Integrated Circuits (ICs) that consume less power, have higher integration, have multi-function capability and are faster.

To achieve higher density, improved performance and lower power consumption, MOS devices have been scaled for more than 30 years (Dutta, 2016). As a result, transistor delay times decrease by more than 30% per technology generation, resulting in doubling of microprocessor performance every two years (Borkar, 1999). Moore's law which states that: "The number of transistors on a chip doubles every 18 months" (Moore, 1965), has been held true for the last 40 years due to rapid progress and scaling (increased integration on a small surface area) of bulk Complementary Metal Oxide Semiconductor (CMOS) transistor technology. This motivates the need for CMOS scaling in the design of low power circuits in scaled technologies (that is, device feature sizes < 100 nm.) to meet low voltage and low power requirements. According to Tyagi (2007), effective channel length, L and gate oxide thickness, tox of 35nm and 1.2nm respectively have been demonstrated in

the 65nm technology mode. This, however, cannot go beyond the limit, effective channel length  $L \leq 10$ nm, which is subject to quantum mechanical tunneling effects which can initiate a damage leading to reliability concerns of the device. Consequently, there are increasing technology and design problems to be solved if Moore's law has to hold. These limitations include standby power leakage, Short Channel Effects (SCEs), parasitic capacitance issues and interconnect issues.

#### 1.2 Problem Statement

With the substantial growth in portable computing and wireless communication in the last five decades, reduction of power dissipation has become a critical issue. Problems of heat removal or cooling are worsening because the magnitude of power dissipated per unit area is growing with the increased integration of more components on a smaller surface area of a chip.

As a result of continued increased integration of more components on a smaller surface area of a chip, the supply voltage,  $V_{dd}$ , has been scaled down in order to keep the power consumption under control. Hence the transistor threshold voltage,  $V_{th}$ , has to be commensurately scaled to maintain a high drive current and achieve performance improvement. However, threshold voltage down-scaling results in an exponential increase in the off-state leakage current known as the subthreshold leakage current,  $I_{sub}$ . This becomes a limiting factor for further down-scaling of the threshold voltage since it determines the power consumption of a chip in its idle state.

This research is intended to model a Silicon-based CMOS transistor with reduced OFF-state subthreshold leakage current,  $I_{sub}$  by varying the threshold voltage,  $V_{th}$ , the channel length, L and the device width, W.

#### 1.3 Objectives:

#### 1.3.1 General Objective

The general objective of this research is to obtain a simplified expression for the offstate subthreshold leakage current of a CMOS device and study the effects of the threshold voltage and device dimensions on it using MATHCAD.

#### 1.3.2 Specific Objectives

The specific objectives of this research are:

- i) To model the OFF-state subthreshold leakage current, I<sub>sub</sub> (OFF).

- ii) To determine the effect of the threshold voltage,  $V_{th}$  on the OFF-state subthreshold leakage current,  $I_{sub}$  (OFF).

- iii) To determine the effect of transistor channel width, W, on the OFF-state subthreshold leakage current,  $I_{sub}$  (OFF).

- iv) To determine the effect of transistor effective channel length, L, on the OFFstate subthreshold leakage current,  $I_{sub}$  (OFF).

- v) To optimize the OFF-state subthreshold leakage current, I<sub>sub</sub> (OFF).

#### 1.4 Justification

Reduction of CMOS device dimensions, by scaling, to accommodate more components on a chip improves performance, increases transistor density, increases transistor switching speed and reduces power consumption. Transistor delay times decrease by more than 30% per technology generation, resulting in doubling of microprocessor performance every two years. Since switching power is proportional to the square of the supply voltage,  $(V_{dd}^2)$ , new processes are tailored towards the reduction of supply voltages. This decrease in  $V_{dd}$  slows down VLSI devices such as logic gates, thus the threshold voltage,  $V_{th}$ , must be lowered to maintain performance. However, continued reduction in the threshold voltage,  $V_{th}$ , results in an exponential increase in the sub-threshold leakage current, I<sub>sub</sub>. Consider an example of a cell phone chip containing one hundred million transistors; if I<sub>sub</sub> (OFF) is a modest 100nA per transistor, the chip would consume so much standby current (10A) that the battery would be drained in minutes without receiving or transmitting any calls. A desktop Personal Computer chip may be able to tolerate this static power but not much more before facing expensive problems with cooling the chip and the system.

It has also been shown that the OFF-state subthreshold leakage current,  $I_{sub}$  (OFF), has increased by about five times per technological generation, for the last three generations. This has been due to the aggressive reduction of device size so that millions of devices can be integrated on a smaller chip area. This will adversely affect most low power devices (microelectronic systems) which usually operate primarily in bursts of activity amid significant periods of inactivity. Standby

subthreshold leakage current reduction can reduce the power dissipation of such devices during these standby periods.

#### **CHAPTER TWO**

#### THEORY AND LITERATURE REVIEW

#### 2.1 Introduction

This chapter discusses the physics of semiconductor devices relevant to the construction, and the basic characteristics of the Metal Oxide Semiconductor Field Effect Transistors (MOSFETs) and the Complementary Metal Oxide Semiconductor (CMOS) transistors. It also looks at the latest literature on the subject area. An insight into the MOSFET as one of the most important electronic devices and its strength that makes it a popular device for Very Large Scale Integration (VLSI) is discussed. MOSFET conduction is discussed based on three different inversion regimes: weak (or subthreshold), moderate and strong inversion. Various subthreshold leakage current mechanisms and models presented during the last two decades are also highlighted.

#### 2.2 The MOSFET Fundamentals

The metal-oxide semiconductor (MOS) transistor has emerged as the most important electronic device, superseding the bipolar junction transistor in sales volume and applications. Its strength derives from its simple structure, low power consumption, especially under steady state direct current (d-c) condition, and low fabrication cost. For these reasons, the MOS transistor continues to be the most popular device for Very Large Scale Integration (VLSI).

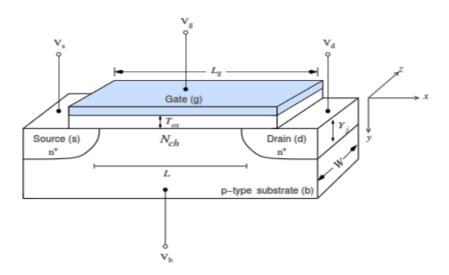

The MOS transistor is a four terminal device in which the lateral current flow is controlled by an externally applied vertical electric field (Yang, 1988). A typical MOS transistor, and some of its important features, is shown in Figure 2.1, where

the four terminals are designated as the Source(s), Gate (g), Drain (d) and Substrate (Bulk, b). However, in most simplified analyses, the effect of the substrate is neglected and the MOS transistor is considered as a three-terminal device.

Figure 2.1: Important MOSFET parameters (NMOS) (Butzen, et.al., 2007).

In earlier fabrications of MOSFETs, the gate electrode consisted of a metal such as Aluminium, a silicon-oxide gate dielectric and the silicon substrate. Nowadays the metal gate electrode and silicon oxide based gate dielectric have been replaced by polycrystalline silicon and high-K material (Gate dielectric material with higher permittivity) such as Hafnium Oxide (HfO<sub>2</sub>) due to its excellent thermodynamic stability on Silicon as well as sufficient conduction and valence band offsets with Silicon (Chan, 2004, Dutta, 2016). There are several important parameters which determine the characteristics of MOSFETs:

- i. Oxide capacitance,  $C_{ox}$  is the capacitance per unit area between the gate metal and the bulk or substrate surface.

- ii. Gate-source voltage,  $V_{gs}$ , is the voltage that is applied between the gate and source to control the operation of the transistor.

- iii. Drain-source voltage,  $V_{ds}$ , is the voltage which is applied between drain and source.

- iv. Threshold voltage,  $V_{th}$ , is the minimum voltage that will induce inversion layer which turns on the transistor.

- v. Drain-Source current,  $I_{ds}$ , is the current that flows between drain and source through the inversion channel induced beneath the gate when the transistor is turned on.

- vi. Oxide layer of thickness,  $t_{ox}$  which separates the gate and the channel.

The source and the drain are formed by adding impurity dopant into the substrate. The semiconductor material in the source and drain regions is doped with a different type of material from that in the substrate. For example, if the substrate is doped using a trivalent atom such as Boron, the source and drain will be doped using a pentavalent atom such as Arsenic. In this case, an n-channel MOSFET (n-MOSFET or NMOS) will be realized. If the doping process described in the preceding example is reversed, a p-channel MOSFET (p-MOSFET or PMOS) will be realized. With no voltage applied to the gate, the two back-to-back p-n junctions between the drain and source prevent current flow in either direction. This is true if the channel length is sufficiently long. When a positive voltage is applied to the gate with respect to the substrate, mobile negative charge is induced in the semiconductor below the semiconductor-oxide interface. The negative carriers provide a conduction channel between the source and the drain. Since the current is controlled by the vertical as well as the lateral electric field, this device is also known as the Insulated Gate Field Effect Transistor (IGFET) (Yang, 1988).

The area between the source and drain beneath the gate, the channel, has a length of L and width W. It is where the inversion layer is formed when sufficient voltage is biased to the gate and drain which then turn on the MOSFET. The oxide layer with a certain thickness,  $t_{ox}$ , separates the gate and the channel.

Basically, three different inversion regimes can be defined for the operation of the MOS transistor. Based on the inversion conditions of the channel, these regimes are called the **weak inversion** or **subthreshold**, the **moderate inversion** and **strong inversion** regimes.

In general, two mechanisms are responsible for the current flow in a transistor; drift and diffusion. Under weak inversion, the channel surface potential is almost constant across the channel and the current flow is determined by diffusion of minority carriers due to a lateral concentration gradient. Under strong inversion, there exists a thin layer of minority carriers at the channel surface and a lateral electric field which causes a drift current to flow. The moderate inversion regime is considered a transition region between weak and strong inversion where both current flow mechanisms coincidentally exist (Yang, 1988).

#### 2.3 The CMOS Transistor

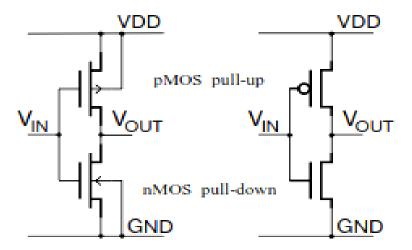

The Complementary Metal Oxide Semiconductor (CMOS) is a widely used type of semiconductor technology. The term "CMOS" refers to both a particular style of digital circuitry design and the family of processes used to implement that circuitry on integrated circuits (chips). A CMOS inverter is an ingenious circuit which is built

from a pair of NMOS and PMOS transistors operating as complementary switches as illustrated in Figure 2.2.

The power supplies for CMOS are  $V_{DD}$  and  $V_{SS}$ , or  $V_{DD}$  and Ground (GND) depending on the manufacturer.  $V_{DD}$  and  $V_{SS}$  are carryovers from conventional MOS circuits and stand for the drain and source supplies respectively. These do not apply directly to CMOS, since both supplies are really source supplies. The outputs of the PMOS and NMOS transistors are complementary such that when the input is low, the output is high, and when the input is high, the output is low. Because of this behavior of input and output, the CMOS circuit's output is the inverse of the input.

Figure 2.2: Schematic diagrams of a CMOS inverter (Taur, et.al., 1998, Sze, et.al., 2007)

Typical CMOS semiconductors use both NMOS (negative polarity) and PMOS (positive polarity) circuits. Since only one of the circuit types is ON at any given time, CMOS chips require less power than chips using just one type of transistor. This makes them particularly attractive for use in battery-powered devices, such as

portable computers. Personal computers also contain a small amount of battery-powered CMOS memory to hold the date, time, and system setup parameters. Equally, CMOS circuitry dissipates less power than logic families with resistive loads. Since this advantage has increased and grown more important, CMOS processes and variants have come to dominate, thus the vast majority of modern integrated circuit manufacturing is on CMOS processes. As of 2010, Computer Central Processing Units (CPUs), with the best performance per watt each year, have been CMOS static logic since 1976 size (Bohr, 2017).

CMOS circuits use a combination of p-type and n-type Metal–Oxide–Semiconductor Field-Effect Transistor (MOSFETs) to implement logic gates and other digital circuits. Although CMOS logic can be implemented with discrete devices for demonstrations, commercial CMOS products are integrated circuits composed of up to 1.3 billion of transistors of both types, on a rectangular piece of silicon of 82 mm<sup>2</sup> die size (Bohr, 2017).

CMOS circuits are constructed in such a way that all PMOS transistors must have either an input from the voltage source or from another PMOS transistor. Similarly, all NMOS transistors must have either an input from ground or from another NMOS transistor. The composition of a PMOS transistor creates low resistance between its source and drain contacts when a low gate voltage is applied and high resistance when a high gate voltage is applied. On the other hand, the composition of an NMOS transistor creates high resistance between source and drain when a low gate voltage is applied and low resistance when a high gate voltage is applied. CMOS accomplishes current reduction by complementing every n-MOSFET with a p-

MOSFET and connecting both gates and both drains together. A high voltage on the gates will cause the n-MOSFET to conduct and the p-MOSFET not to conduct, while a low voltage on the gates causes the reverse. This arrangement greatly reduces power consumption and heat generation. However, during the switching time, both MOSFETs conduct briefly as the gate voltage goes from one state to another. This induces a brief spike in power consumption and becomes a serious issue at high frequencies.

#### 2.4 Leakage current mechanisms in scaled CMOS devices:

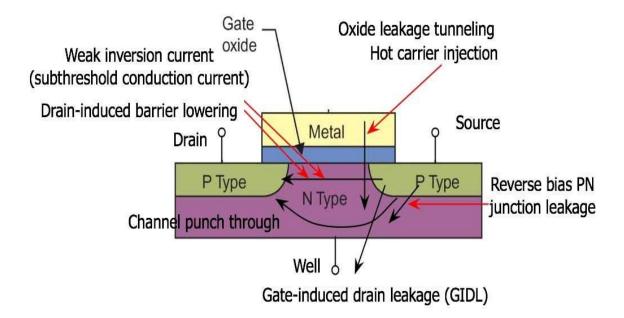

Generally, in nanometer CMOS circuits, the main leakage current mechanisms are gate tunneling, reverse-biased junction band-to-band tunneling (BTBT) and subthreshold leakage currents, as shown in Figure 2.3.

Figure 2.3: Major leakage mechanisms in MOS transistors (Butzen, et.al., 2007).

#### **2.4.1 Gate Oxide Tunneling Current**

The aggressive scaling of devices in the nanometer regime increases Short Channel Effects (SCEs) such as Drain Induced Barrier Lowering (DIBL) (cf. appendix) and threshold voltage, V<sub>th</sub>, roll-off. To control these SCEs, the oxide thickness is made thinner. However, this gives rise to high electric fields resulting in a high direct-tunneling current through the transistor gate insulator (Xu, *et.al.*, 2004).

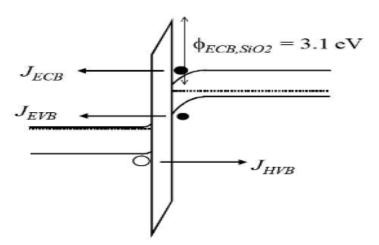

There are three major gate leakage mechanisms in a MOS structure. The first one is the electron conduction-band (ECB) tunneling, where electrons tunnel from the conduction band of the substrate to the conduction band of the gate (or vice-versa). The second one is the electron valence-band (EVB) tunneling, where electrons tunnel from the valence band of the substrate to the conduction band of the gate. The last one is the hole valence-band (HVB) tunneling, where holes tunnel from the valence band of the substrate to the valence band of the gate (or vice-versa), Figure 2.4.

Figure 2. 4: Three mechanisms of gate dielectric tunneling leakage (Cao, 2000).

In figure 2.4,  $J_{ECB}$  is the Electron-Conduction Band tunneling current density,  $J_{EVB}$  the Electron-Valence Band tunneling current density,  $J_{HVB}$  the Hole-Valence-Band tunneling current density and  $\phi_{ECB,SiO2}$  is the Electron-Conduction Band gate oxide potential barrier height.

The tunneling of electrons (or holes) from the bulk and source or drain overlap regions through the gate oxide potential barrier into the gate (or vice-versa) is referred to as gate oxide tunneling current. This phenomenon is related with the MOS capacitance concept.

Each mechanism is dominant or important in different regions of operation for NMOS and PMOS transistors. For each mechanism, gate leakage current can be modeled by (Xu, *et.al.*, 2004, Roy, *et.al.*, 2007, Vijayalakshmi, 2017),

$$I_{\text{gate}}=\text{W.L.A.} \left[\frac{V_{ox}}{t_{ox}}\right]^{2} e^{\left[\frac{-B\left[1-\left[1-\frac{V_{ox}}{\phi_{ox}}\right]^{3/2}\right]}{\frac{V_{ox}}{t_{ox}}}\right]}$$

(2.1)

where W and L are the effective transistor width and lengths respectively,  $V_{ox}$  is the voltage drop across the oxide,  $t_{ox}$  is the oxide thickness and  $\hbar$  is reduced Planck's constant. The parameters A and B in equation (2.1) are defined by,

$$A = \frac{q^3}{16\pi^2\hbar\phi_{0x}} \tag{2.2}$$

and,

$$B = \frac{4\pi\sqrt{2m_{ox}\phi_{ox}^{3/2}}}{3\hbar a}$$

(2.3)

where  $m_{ox}$  is the effective mass of the tunneling particle,  $\phi_{ox}$  is the tunneling barrier height and q is the electron charge.

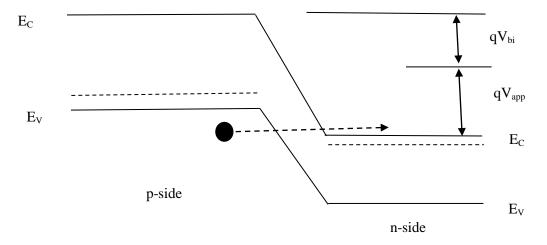

#### 2.4.2 Band-To-Band Tunneling (BTBT) Current

The MOS transistor has two p-n junctions; drain and source to well junctions. These junctions are typically reverse biased, causing a p-n junction leakage current. This current is a function of the junction area and doping concentration (Xu, *et.al.*, 2004, Butzen, *et.al.*, 2007). When 'n' and 'p' regions are heavily doped, BTBT leakage dominates the reverse biased p-n junction leakage mechanism.

A high electric field across a reverse-biased p-n junction causes a current flow through the junction due to tunneling of electrons from the valence band of the p-region to the conduction band of the n-region, as illustrated in Figure 2.5.

Figure 2.5: BTBT in reverse-biased p-n junction (Vijayalakshmi, 2017).

Tunneling current occurs when the sum of voltage drop across the junction, the applied reverse-bias voltage  $(V_{app})$  and the built-in voltage  $(V_{bi})$  is larger than the

band-gap potential. The tunneling current density through a silicon p-n junction is given by (Roy, *et.al.*, 2007),

$$J_{BTBT} = M. \frac{EV_{app}}{E_g^{1/2}} e^{\left[\frac{-N.E_g^{3/2}}{E}\right]}$$

(2.4)

The parameters M and N in equation (2.4) are defined by,

$$M = \frac{\sqrt{2m^*q^3}}{4\pi^3\hbar^2} \tag{2.5}$$

and,

$$N = \frac{4\sqrt{2m^*}}{3\hbar q} \tag{2.6}$$

where  $m^*$  is the effective mass of the electron,  $E_g$  is the energy-band gap,  $V_{app}$  is the applied reverse-bias and E is the electric field at the junction.

Band-to-Band tunneling leakage, negligible in current processes when compared to the subthreshold and gate oxide leakages, starts to be taken into account in 25nm technologies (Xu, *et.al.*, 2004, Mukhopadhay, 2005). The junction tunneling current depends exponentially on the junction doping and the reverse bias across the junction. Forward body bias can be used to reduce the band-to-band tunneling leakage.

#### 2.4.3 Punchthrough Current

The punchthrough current is the leakage current from the source to the drain via the silicon substrate which is significantly reduced by lowering the temperature. This is

due to the fact that the punchthrough current is mainly due to thermionic emission between the source and the drain.

The punchthrough current,  $I_p$ , is given by, (Butzen, *et.al.*, 2007);

$$I_p = I_o e^{\frac{-\Phi}{kT}} \tag{2.7}$$

where  $\Phi$  is the source-to-drain potential barrier height and the parameter  $I_o$  is the current at threshold which is dependent on process and device geometry. It is typically extracted by simulation but can also be calculated from the equation,

$$I_{o} = \frac{W\mu_{o}C_{ox}V_{T}^{2}e^{1.8}}{L}$$

(2.8)

The  $e^{1.8}$  term was found empirically (Sheu, 1987).  $C_{ox}$  is the gate oxide capacitance and  $\mu_0$  is the carrier mobility. The parameter  $V_T$  is known as the thermal voltage and is expressed as,

$$V_{T} = \frac{kT}{q} \tag{2.9}$$

where k is the Boltzmann's constant and T is the absolute temperature.

Thus, the punchthrough current is thermally generated and is strongly reduced at low temperature. This phenomenon is critical in the subthreshold region where the presence of low amplitude leakage currents is easily observable. This feature demonstrates that the operation at low temperature is an effective way to reduce the parasitic punchthrough leakage current in MOSFETs even though their operation is not well optimized at room temperature.

#### 2.4.4 Subthreshold Leakage Current

Subthreshold leakage current,  $I_{sub}$ , is defined as the drain-to-source leakage current when the transistor is OFF (Xu, *et.al.*, 2004, Deepaksubramanyan, *et.al.*, 2007, Vijayalakshmi, 2017). It occurs between drain and source when the transistor is operating in the weak inversion region, that is, the gate voltage,  $V_g$ , is lower than the threshold voltage,  $V_{th}$ ; ( $V_g < V_{th}$ ). In this region, supply voltage has been reduced so that the dynamic power consumption is controlled. The minority carrier concentration is almost zero, and the channel has no horizontal electric field, but a small longitudinal electric field appears due to the drain-to-source voltage. In this situation, the carriers move by diffusion between the source and the drain of the MOS transistor. Therefore, the subthreshold leakage current is dominantly due to the diffusion of carriers and it varies exponentially with both the gate-to-source and threshold voltages.

To maintain a high drive current capability, the threshold voltage,  $V_{th}$ , has to be reduced too. This, in turn, results in increase in the subthreshold leakage current. This is due to the fact that current does not drop abruptly to zero when  $V_{gs} = V_{th}$ . Furthermore, the drain current is not zero at zero gate voltage (and large drain voltages), indicating that the gate has lost control of shutting off the device (Yang, 1988). Instead, the current decays off in an exponential fashion when  $V_{gs} < V_{th}$ . Thus, the output current cannot be turned OFF and the transistor can no longer function as a switch. However, this soft breakdown (exponential current decay) is not seen in long channel devices.

The threshold voltage,  $V_{th}$ , for a MOS device is the minimum voltage that will induce inversion layer which turns on the transistor. In order to take into account non-uniform substrate doping, the following standard threshold model (Gu, *et.al.*, 1996) was proposed,

$$V_{th} = V_{fb} + \phi_s + K_1 \sqrt{\phi_s - V_{bs}} - K_2 [\phi_s - V_{bs}] - \eta V_{ds}$$

(2.10)

where  $\phi_s$  is the surface-inversion potential,  $K_1$  and  $K_2$  together model the body effect phenomenon,  $V_{ds}$  is the drain-to-source voltage,  $V_{bs}$  is the body bias voltage,  $V_{ds}$  is the Drain Induced Barrier Lowering (DIBL) coefficient and  $V_{fb}$  is the flat-band voltage. In an idealized MOS structure, it is assumed that the energy-band diagram is flat when the gate voltage is zero. In practice, however, this condition is not realized because of unavoidable work function difference and charges in the oxide and surface states (Yang, 1988). To achieve the flat-band condition for an NMOS, a negative gate voltage is applied to lower the electric field distribution until the charge is reduced to zero at the silicon surface. The gate voltage required to achieve the flat-band condition is known as the flat-band voltage,  $V_{fb}$ .

At values of the gate-source voltage,  $V_{gs}$  below the threshold voltage,  $V_{th}$ , the inversion electron concentration  $(n_s)$  is small but nonetheless can allow a small leakage current to flow between the source and the drain,  $I_{ds}$ . The differential equation for the surface-inversion potential,  $\varphi_s$  with respect to the gate-source voltage is given by (Mookerjea, 2009),

$$\frac{d\varphi_S}{dV_{qS}} = \frac{C_{ox}}{C_{ox} + C_{dep}} \equiv \frac{1}{n}$$

(2.11)

where  $\varphi_s$  is the surface-inversion potential,  $C_{ox}$  is the gate oxide capacitance,  $C_{dep}$  is the capacitance of the depletion layer, n is the Subthreshold swing coefficient and  $V_{gs}$  is the gate-source voltage

Considering the Berkeley Short-Channel IGFET Model for MOS transistors (BSIM MOS), (Sheu, 1987, Gu, *et.al.*, 1996, Manisha, 2011, Singh, *et.al.*, 2013, Vijayalakshmi, 2017), the subthreshold leakage current for a MOSFET device is expressed by,

$$I_{\text{sub}} = I_{\text{o}} \cdot e^{\frac{V_{gs} - V_{th}}{nV_T}} \left[ 1 - e^{\frac{-V_{ds}}{V_T}} \right]$$

(2.12)

where  $V_{th}$  is the threshold voltage,  $V_{ds}$  and  $V_{gs}$  are drain-to-source and gate-to-source voltages, respectively and n is the subthreshold swing coefficient, for a long channel uniformly doped device given by,

$$n = 1 + \frac{c_b}{c_{ox}} \tag{2.13}$$

where the parameters  $C_b$  and  $C_{ox}$  are the bulk (substrate) and the gate oxide capacitances, respectively. These are expressed by equations (2.14) and (2.15) respectively.

$$C_b = \frac{\varepsilon_{si}}{\omega_d} \tag{2.14}$$

and,

$$C_{ox} = \frac{\varepsilon_{ox}}{t_{ox}} \tag{2.15}$$

where  $\varepsilon_{ox}$  and  $\varepsilon_{si}$  denote the dielectric constants of the oxide and silicon respectively,  $\omega_d$  is the depletion width under the channel, and  $t_{ox}$  is the gate oxide thickness.

The practical definition of  $V_{th}$  in experimental studies is the gate-source voltage  $V_{gs}$  at which the drain to source current,  $I_{ds}$ , in nano-Amperes (nA) is given by,

$$I_{ds}(nA) = 100 \times \frac{W}{L} \times e^{\frac{q(V_{gs} - V_{th})}{nkT}}$$

(2.16)

The 100 value in equation (2.16) is the value of the current at threshold  $I_o$ , in nA, and it is derived from,

$$I_{o} = \frac{W\mu_{o}C_{ox}V_{T}^{2}e^{1.8}}{L}$$

(2.8)

The carrier mobility  $\mu_o$  is the proportionality constant between the applied electric field (in V/cm) and the resulting velocity of the carriers (in cm/sec). The intrinsic values (for pure silicon) of the mobility for electrons and holes at room temperature (T= 300K) are,

$\mu_n=1350 cm^2/V \cdot s$  (for electrons) and  $\mu_p=480 cm^2/V \cdot s$  (for holes). The fact that holes are more sluggish than electrons has some influence on relative sizes of nMOS and pMOS transistors. The gate-oxide-channel structure forms a capacitor. The gate-oxide capacitance per unit area can be calculated from the equation (2.15), where,  $\varepsilon_{ox}=0.351 pF/cm$  is the permittivity (a dielectric constant) of SiO<sub>2</sub>. Note that this capacitance is inversely proportional to the thickness of the silicon-dioxide layer. The oxide thickness and the resulting gate capacitance per unit area are parameters specified by the technological process of fabrication of CMOS transistors.

For example, consider a typical 65 nm technology process nMOS transistor at Vgs= 1.0 V, where the gate oxide thickness,  $t_{ox}$ , used was 194 nm and  $V_T^2$  at room temperature was  $6.76 \times 10^{-6} \text{ V}^2$ , (Weste, *et.al.*, 2016), then,

$$C_{ox} = \frac{\varepsilon_{ox}}{t_{ox}} = \frac{3.51 \times 10^{-13}}{1.94 \times 10^{-7}} = 1.81 \times 10^{-6} \text{F/cm}^2$$

(2.17)

and,

$$\mu_o C_{ox} V_T^2 e^{1.8} = 1350 \times 1.81 \times 10^{-6} \times 6.76 \times 10^{-6} \times 6.0497 = 9.99 \times 10^{-8} \text{ A}$$

$$\approx 100 \text{ nA} \tag{2.18}$$

In practice, this value (2.18) is usually set by CMOS manufacturing Companies, during fabrication, to either 100 nA or 200 nA. The choice of this value by a Company to be 100 nA or 200 nA depends on the carrier mobility,  $\mu_0$ , the gate oxide capacitance,  $C_{ox}$ , the device geometry and the thermal voltage,  $V_T$  the Company has adopted for fabrication of the transistor. For lower subthreshold leakage current,  $I_{sub}$ , a lower value is desirable, hence the choice of 100 nA in equation (2.16).

The empirical value of the channel length L, is 10 nm; which is the minimum value of L before quantum mechanical tunneling effects set in, while that of the channel width W= 7 nm; which approximates the current design minimum device width, and  $V_{gs}$  =0. The current through the device is measured for values of  $V_{th}$ = 0 to 300 mV. The 300 mV value approximates the upper edge of the subthreshold region for the CMOS devices (Deepaksubramanyan, *et.al.*, 2007, Weste, *et.al.*, 2016).

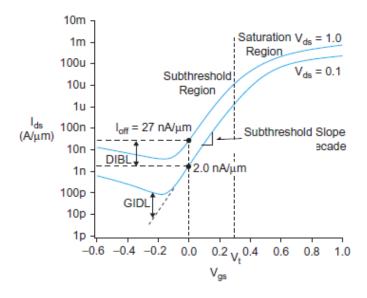

On a graph of  $I_{ds}$  versus Vgs, with logarithmic (base 10) axis for  $I_{ds}$ , the subthreshold slope is found as the straight-line approximation of the subthreshold current, normally expressed in units of decades/mV. The Subthreshold swing is the inverse of this slope and is expressed in units of mV/decade. Ideally, it is assumed that the current will drop as fast as possible once  $V_{gs} < V_{th}$ . However, in real transistors, current does not abruptly cut off below threshold voltage, but rather drops off exponentially as shown in Figure 2.6,

Figure 2.6: I-V characteristics of a 65 nm nMOS transistor at 70°C on a log scale (Weste, *et.al.*, 2016)

When the gate voltage,  $V_{gs}$  is high, the transistor is strongly ON. When the gate voltage falls below the threshold voltage, that is  $V_{gs} < V_{th}$ , the exponential decline in current appears as a straight line on a semi-logarithmic plot of  $I_{ds}$  against  $V_{gs}$ . The inverse of the slope of this line is known as the subthreshold swing, S, in mV/decade (Roy, *et.al.*, 2007, Manisha, 2011, Singh, *et.al.*, 2013, Weste, *et.al.*, 2016), given by,

$$S = \left[ \frac{d(log_{10}I_{ds})}{dV_{gs}} \right]^{-1}$$

(2.19)

This is alternatively defined by,

$$S = n \left[ \frac{kT}{q} \right] \ln 10 \tag{2.20}$$

Since  $\ln 10 = 2.3$ ,

$$S = 2.3n \frac{kT}{q} \tag{2.21}$$

Substituting equation (2.13) into equation (2.21) for n, the subthreshold swing, S is found to be,

$$S = 2.3 \frac{kT}{q} \left[ 1 + \frac{C_b}{C_{ox}} \right] \tag{2.22}$$

The subthreshold swing describes the exponential behavior of the current as a function of voltage. It also indicates how effectively the transistor can be turned off, that is, the rate of decrease of I<sub>OFF</sub>, when V<sub>gs</sub> is decreased below V<sub>th</sub>. Practically, S can range from 70 to 120 mV/decade for a bulk CMOS process, while the subthreshold swing coefficient, n ranges between 1 and 2 (Deepaksubramanyan, *et.al.*, 2007, Weste, *et.al.*, 2016).

As device dimensions and the supply voltage are scaled down to enhance performance, power efficiency and reliability, subthreshold leakage current may limit the scalability of the supply voltage.

### 2.5 Subthreshold Leakage Current Models:

Several subthreshold leakage current models have been presented during the last two decades. A typical subthreshold leakage model, reported by Narendra, *et.al.* (2006) is given by,

$$I_{sub} = WI_1 \cdot 10^{-\frac{1}{n}(\Delta Vgs + \eta \Delta Vds + \Upsilon \Delta Vbs)}$$

(2.23)

where  $I_1$  is the leakage current of a single transistor of unit width in an off- state device with  $V_{gs}=V_{bs}=O$  V (zero volts) and  $V_{ds}=V_{dd}$ .  $\Delta V_{gs}$ ,  $\Delta V_{bs}$  and  $\Delta V_{ds}$  are the gate-drive, body bias and drain to source voltages, respectively, reduced based on the above mentioned conditions,  $\eta$  is the Drain- Induced Barrier Lowering (DIBL) coefficient and  $\Upsilon$  is the linearized body effect coefficient. Equation (2.23) is obtained having made the assumption that the resulting drain-source Voltage,  $V_{ds}$  will be such that,

$$V_{ds} > \frac{3kT}{q} \tag{2.24}$$

Another subthreshold leakage current model was reported by Gu, et.al. (1996) and is given by,

$$I_{\text{sub}} = I_{\text{o}} \cdot e^{\frac{V_{gs} - V_{th}}{nV_T}} \left[ 1 - e^{\frac{-V_{ds}}{V_T}} \right]$$

(2.12)

Finally, another subthreshold leakage current model was reported by Roy, *et.al.* (2007) is given by,

$$I_{sub} = I_o W e^{\frac{Vgs - (Vtho - \eta Vds - YVbs)}{nV_T}} \left(1 - e^{\frac{-Vds}{V_T}}\right)$$

(2.25)

where  $V_{tho}$  in equation (2.25) is the zero-bias threshold voltage.

In this thesis, a more simplified model is derived (refer to equation 3.14) which is then analysed to show how transistor features can be varied to obtain a transistor with reduced OFF-state subthreshold leakage current.

### 2.6 Some Existing Techniques for Subthreshold Leakage Current reduction:

This section gives a brief highlight of some existing techniques for subthreshold leakage current reduction advanced in the last two decades. Equation (2.12) (Sheu, 1987, Gu, et.al., 1996, Manisha, 2011, Singh, et.al., 2013, Vijayalakshmi, 2017), shows that exponential decreases in the subthreshold leakage current,  $I_{sub}$ , are possible by either increasing the threshold voltage,  $V_{th}$  or by decreasing  $V_{gs}$ . Alternatively, modifying transistor structures, such as by the use of stacks, decreasing  $V_{gs}$  in standby mode by raising the source voltage through switched-source-impedance, biasing the body voltage to change  $V_{th}$ , using dual-threshold or multi-threshold CMOS techniques, overdriving the gate voltage of sleep devices in active mode, and varying doping levels can be used to respond to the challenge of decreasing Subthreshold Leakage current (Horiguchi, et.al., 1993, Xu, et.al., 2004, Dutta, 2016). Existing techniques for subthreshold leakage reduction explore some of these options.

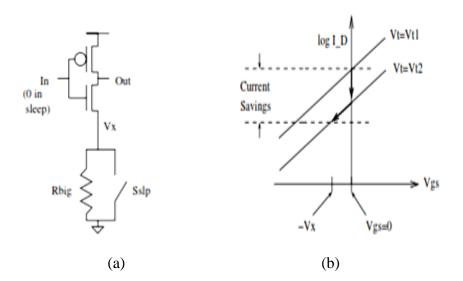

### 2.6.1 Switched Source Impedance

One obvious method for reducing leakage current is to decrease  $V_{gs}$  in standby mode by raising the source voltage through switched-source-impedance CMOS (Horiguchi, *et.al.*, 1993). In this approach, a passive resistor is switched in between a gate's source nodes and ground during standby mode. During active mode, the resistor is shorted out so that there is no additional delay penalty.

The presence of the resistor in standby mode introduces a positive voltage at  $V_X$  due to the leakage current through  $R_{big}$  as seen in Figure 2.7a.

Figure 2.7: Switched-Source-Impedance, (a) Circuit Example, (b) Savings (Horiguchi, et.al., 1993)

The voltage  $V_X$  reduces leakage current in two ways. First, the increased source voltage of the NMOS device causes an increase in the threshold voltage due to the well-known equation (2.10) (Sheu, 1987, Manisha, 2011, Singh, *et.al.*, 2013). This higher  $V_{th}$  causes a shift in the current- $V_{gs}$  curve in Figure (2.7b) from  $V_{th} = V_{th1}$  to

$V_{th}=V_{th2}$ . Furthermore, the increased  $V_X$  reduces  $V_{gs}$  of the NMOS device, causing the operating point to shift downward along the current- $V_{gs}$  curve. The combination of these two effects lowers the standby leakage current. In practice, switched-source impedance circuits are rare because the resistor must be large and resistor placement depends on knowing the standby state of every gate. Since there is no perfect switch, the resistance of the switch often replaces the explicit resistor for this technique.

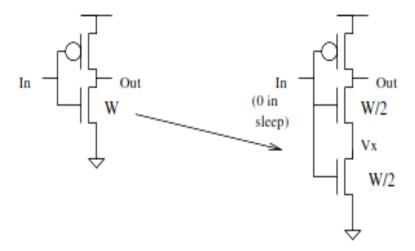

### 2.6.2 Stack Effect

A similar and more practical technique for subthreshold leakage reduction takes advantage of the stack effect. The term *stack effect* refers to the reduction of subthreshold leakage by stacking multiple FETs in series (Xu, *et.al.*, 2004, Saxena, *et.al.*, 2013, Sharma, *et.al.*, 2013). Figure (2.8) shows a case of artificially introducing the stack effect to an inverter, but stacks of transistors occur naturally in many logic gates (*that is*, NAND).

Figure 2.8: Artificial Creation of Stack Effect (Saxena, et.al., 2013).

The stack effect provides leakage reduction in the same way as switched-source-impedance. The last device in the stack essentially appears as impedance to any leakage current, so the voltage  $V_X$  becomes non-zero.

At that point, the effects shown in Figure (2.7b) occur as previously described. Notice that the imposed stack effect approach is essentially the switched-source-impedance approach without the resistor. This approach just uses the resistance of the non-ideal switching FET in an OFF state.

Designers take advantage of the stack effect in two ways. First, one can exploit natural stacks in a circuit by determining an input vector at design time that turns off stacks of devices. Several algorithms exist for applying test vectors to a circuit at design time to find the vector that generates the lowest leakage current (Xu, *et.al.*, 2004, Saxena, *et.al.*, 2013). When the circuit enters standby mode, this low-leakage vector is multiplexed into the circuit inputs.

Artificial introduction of stacks to a circuit (Narendra, et.al., 2006) can enhance the gains from the vector-finding method of leakage reduction. In this approach, stacks are introduced to gates off of the critical path (Figure 2.8). While slower itself, the new gate presents the same capacitive load at its input, so it does not slow down previous gates. This method trades off speed on non-critical paths and design time for reduced leakage. A new model for determining the savings, introduced by

forcing stacks, allows designers to determine the usefulness of the approach for a given technology (Narendra, *et.al.*, 2006, Sharma, *et.al.*, 2013).

### 2.6.3 Body Biasing

An entirely different approach to reducing subthreshold leakage biases the body voltage to change  $V_{th}$ . In order to maintain the cut off condition for all the substrate-to-channel junctions, the substrate is usually connected to the most negative power supply in an NMOS circuit (to the most positive in a PMOS circuit). The resulting reverse bias voltage between the source and body will have an effect on device operation. The reverse bias voltage will widen the depletion region. This will in turn reduce the channel depth (Maheshwari, 2014). There are many angles taken to use this technique, such as the Variable Body Biasing Technique (VBBT) (Yadav, *et.al.*, 2015), but they all require isolation of the bulk for different FETs (as in a triple well process).

### 2.6.4 Dual-Threshold CMOS

Dual-threshold CMOS techniques use FETs having two thresholds to reduce leakage currents. The most straightforward application of dual-threshold CMOS uses all low  $V_{th}$  FETs on the critical path and high  $V_{th}$  FETs off of the critical path. The high  $V_{th}$  devices placed at design time reduce leakage while increasing delay off of the critical path. The placement of these devices can become complicated since the high  $V_{th}$  devices can slow down parts of the circuit enough to create new critical paths (Sreenivasulu, 2013).

Nevertheless, several algorithms exist for that purpose that maintains a high supply voltage for gates on the critical path and by using a low supply voltage for the gates

off the critical path (Sundararajan, *et.al.*, 1999). One advantage of dual-threshold CMOS is that the leakage savings occur in both active and standby modes. Disadvantages include more complicated design time and the inability to stop critical path leakage during standby mode.

Dual-threshold CMOS is particularly useful for some special logic styles. For example, domino logic can use high  $V_{th}$  devices on the precharge path (Kao, et.al., 2002, Sreenivasulu, 2013). All of the pull-down paths remain fast because of the low  $V_{th}$  devices, but each path between the rails contains at least one high  $V_{th}$  device. This allows the tradeoff of precharge time with reduced leakage.

### 2.6.5 Multi-Threshold CMOS (MTCMOS)

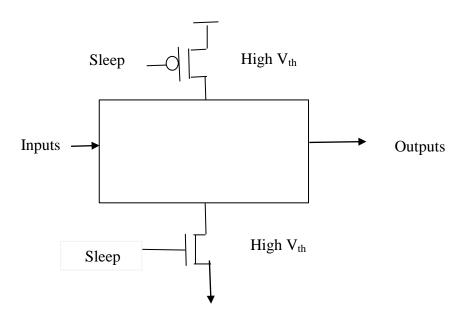

Multi-Threshold CMOS (MTCMOS) refers to a circuit technique that uses a high  $V_{th}$  footer and/or header FET to sever a circuit from the power rails as illustrated in Figure 2.9 (Mutoh, 1995, Yadav, *et.al.*, 2015).

Figure 2.9: MTCMOS Schematic (Kumar, et.al., 2013).

Similar approaches have been applied to caches (Powell, 2001, Anis, *et.al.*, 2003, Kumar, *et.al.*, 2013) and to DRAMs (Sakata, 1994).

In the active mode, the high  $V_{th}$  switches are ON to enable regular circuit operation. Turning OFF the high  $V_{th}$  devices in standby mode places at least one high  $V_{th}$  FET on each path from power to ground, thereby reduces the leakage current significantly. Small sleep devices reduce the leakage current in standby mode but slow down transitions in active mode. The loss of performance occurs because smaller sleep devices sink less current through to ground.

This exacerbates the bouncing created at the virtual rails and effectively pinches  $V_{ds}$  for the low  $V_{th}$  circuit. Furthermore, this rail bounce depends on the discharge pattern of the circuit, so it can be difficult to predict worst-case performance.

Combinational logic blocks only need a sleep device on one rail, but sequential MTCMOS circuits are more complicated. Simply disconnecting a circuit from the rails in standby destroys any state previously stored in that circuit. Special care is necessary to retain state in MTCMOS sequential circuits. Despite some of the design difficulties, MTCMOS techniques appear to be viable for reducing leakage currents in new technologies.

### 2.6.6 Boosted Gate MOS (BGMOS) and Super Cut-Off CMOS (SCCMOS)

Two additional proposals for reducing leakage basically increase the effectiveness of MTCMOS sleep transistors. The Boosted Gate MOS (BGMOS) approach (Inukai, 2000) suggests that overdriving the gate voltage of sleep devices in active

mode can reduce the area devoted to sleep devices. The overdriven (above  $V_{dd}$ ) gate voltage enables a smaller device to sink the required amount of current in active mode while still effectively stemming the leakage current in standby mode. A similar approach called Super Cut-off CMOS (SCCMOS) advocates under-driving gate voltages in standby mode (Kawaguchi, *et.al.*, 2000, Kumar, *et.al.*, 2013). For example, an NMOS sleep device would be turned OFF in standby mode with a negative gate voltage rather than a gate voltage of 0 volts. From equation (2.11), we see that the negative gate voltage provides exponentially decreasing leakage current through the sleep device.

Despite the existence of these techniques, problems of heat removal or cooling, aggravated by increasing subthreshold leakage current, continue worsening because the magnitude of power dissipated per unit area keeps on growing with the increased integration of more components on a smaller surface area of a chip. Some of the techniques, like the use of stacks, results in slower switching speeds for the devices making it unsuitable for use in devices where high switching speed is required.

### **CHAPTER THREE**

### METHODOLOGY

### 3.1 Introduction

In this chapter, the expression used to examine the effect of varying the threshold voltage,  $V_{th}$ , the transistor's channel width, W and its effective length, L on off-state the subthreshold leakage current,  $I_{sub}$  (OFF) was derived. The obtained expression was then evaluated using MATHCAD.

### 3.2 Derivation of the simulation equation

In a practical CMOS transistor, the drain-source current,  $I_{ds}$  is exponentially proportional to the surface inversion potential,  $\varphi_s$ , that is,

$$I_{ds} \propto e^{\frac{q\varphi_s}{kT}}$$

(3.1)

Now, the derivative of the surface inversion potential,  $\varphi_s$ , against the gate to source voltage,  $V_{gs}$  is given by,

$$\frac{d\varphi_s}{dV_{qs}} = \frac{C_{ox}}{C_{ox} + C_{dep}} \equiv \frac{1}{n}$$

(2.11)

Rewriting equation (2.11) implies that,

$$n = 1 + \frac{c_{dep}}{c_{ox}} \tag{3.2}$$

where  $C_{dep}$  is the capacitance of the depletion layer.

Integrating equation (2.11), that is,

$$\int d\varphi_s = \frac{1}{n} \int dV_{gs} \tag{3.3}$$

or,

$$\varphi_s = constant + \frac{v_{gs}}{n} \tag{3.4}$$

where the constant parameter in equation (3.4), is,

$$constant = \frac{-V_{th}}{n} \tag{3.5}$$

then by using equations (3.4) and (3.5) in the index of the exponential of proportionality (3.1), results in,

$$\propto e^{q\left(\frac{-V_{th}}{n} + \frac{V_{gs}}{n}\right)/kT}$$

(3.6)

and,

$$I_{ds} = I_0 e^{q\left(\frac{-V_{th}}{n} + \frac{V_{gs}}{n}\right)/kT}$$

(3.7)

where,

$$I_{o} = \frac{W\mu_{o}C_{ox}V_{T}^{2}e^{\frac{qV_{gs}}{nkT}}}{L}(1-e^{\frac{-V_{ds}}{V_{T}}})$$

(3.8)

Using equations (2.9) and (2.20), equation (3.8) simplifies to,

$$I_{o} = \frac{W\mu_{o}C_{ox}V_{T}^{2}e^{\frac{V_{gsln10}}{S}}}{L}(1-e^{\frac{-V_{ds}}{V_{T}}})$$

(3.9)

Now, at threshold,

$$I_{o} = \frac{W\mu_{o}C_{ox}V_{T}^{2}e^{1.8}}{L}$$

(2.8)

When evaluated gives (refer to results 2.17 and 2.18),

$$I_{o} = \frac{100 W}{L} \tag{3.10}$$

Now, from equations (2.8), (2.9) and (3.7),

$$I_{ds} = I_{o} e^{\left(\frac{(V_{gs} - V_{th}) \ln 10}{S}\right)}$$

(3.11)

When the CMOS device is in standby mode the leakage current,  $I_{ds}$ , is also referred to as the subthreshold leakage current,  $I_{sub}$  (also denoted as  $I_{OFF}$ ). In this OFF-state,  $V_{gs} = 0$ , thus equation (3.11) is rewritten as,

$$I_{sub} = I_o e^{\left(\frac{-V_{th} \ln 10}{S}\right)}$$

(3.12)

This simplifies to,

$$I_{sub} = I_o \times 10^{\frac{-V_{th}}{s}} \tag{3.13}$$

Thus by using equations (3.10) and (3.13),

$$I_{sub} = 100 \times \frac{W}{L} \times 10^{\frac{(-V_{th})}{s}} \tag{3.14}$$

Thus, the characteristics of subthreshold leakage current in the OFF state,  $I_{sub}$  (in nA) when the threshold voltage,  $V_{th}$  and device dimensions (channel length, L and width, W) are varied, can be determined by the model equation (3.14).

### **CHAPTER FOUR**

### **RESULTS AND DISCUSSIONS**

### 4.1 Introduction

In this chapter, the results obtained from modelling a CMOS device based on the variations in the threshold voltage,  $V_{th}$ , transistor effective width, W and the transistor's effective channel length, L and their effects on the value of the OFF-state subthreshold leakage current,  $I_{sub}$  are discussed and presented. The model equation (3.13) is analyzed by varying the subthreshold swing, S through three different sets of values.

# 4.2 Effect of threshold voltage, $V_{th}$ on the OFF-state subthreshold leakage current, $I_{sub}$

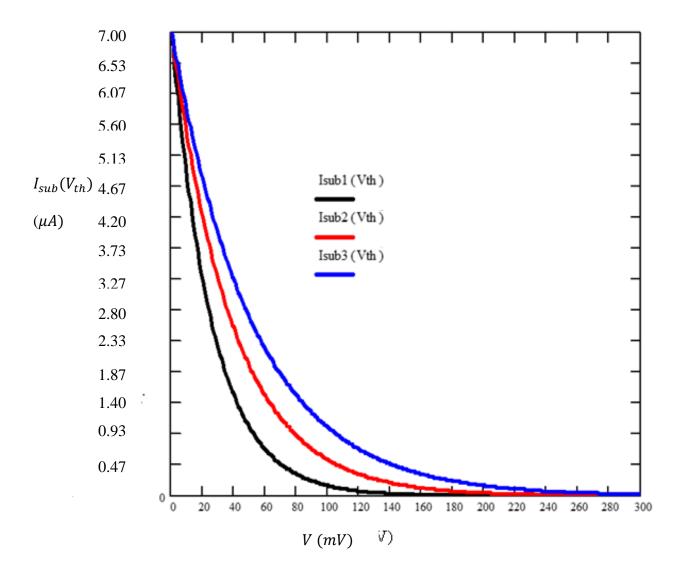

The subthreshold swing, S in equation (3.14) is varied through S= 60, 90 and 120 mV/decade while the values of W and L are set at 7 nm and 10 nm respectively. Substituting the values of S, W and L respectively, into the model equation (3.14), three equations (4.1a), (4.1b) and (4.1c) are obtained.

$$I_{sub1}(OFF)(A) = 100 \times 7.0 \times 10^{-10} \times 10^{\frac{-V_{th}}{60}}$$

(4.1a)

$$I_{sub2}(OFF)(A) = 100 \times 7.0 \times 10^{-10} \times 10^{\frac{-V_{th}}{90}}$$

(4.1b)

$$I_{sub3}(OFF)(A) = 100 \times 7.0 \times 10^{-10} \times 10^{\frac{-V_{th}}{120}}$$

(4.1c)

In the MATHCAD worksheet, the variable(s) and the function that depends on the behaviour of the variables are initially defined by entering,

$$V_{th}:0;300$$

(4.1d)

Input (4.1d) defines the range of  $V_{th}$  over which  $I_{sub}(A)$  is passing through the device. The leakage current  $I_{sub}$  is a function of  $V_{th}$ , and it is defined from equations (4.1a), (4.1b) and (4.1c) as,

$$I_{sub1}(V_{th}): 100 * 7.0 * 10^{-10} * 10^{\land} - V_{th}/60$$

(4.1e)

$$I_{sub2}(V_{th}): 100 * 7.0 * 10^{-10} * 10^{\land} - V_{th}/90$$

(4.1f)

$$I_{sub3}(V_{th}): 100 * 7.0 * 10^{-10} * 10^{\land} - V_{th}/120$$

(4.1g)

The data and its graph were obtained by inputting the commands,

$$V_{th} = I_{sub1}(V_{th}) = I_{sub2}(V_{th}) = \text{and } I_{sub3}(V_{th}) =$$

(4.1h)

Figure 4.1 shows plots of the data obtained from equations (4.1e), (4.1f) and (4.1g) where the leakage current,  $I_{sub}$  is plotted against the threshold voltage,  $V_{th}$  for different values of the subthreshold swing, S.

Figure 4.1: Variation of  $I_{sub}$  with  $V_{th}$ .

These graphs show that the leakage current,  $I_{sub}$  decreases exponentially with increase in the threshold voltage,  $V_{th}$ . The graphs also show that for a scaled CMOS device, whose channel length, L= 10 nm, the channel width, W= 7 nm,  $V_{gs}$  =0 (OFF-state) and the subthreshold swing, S= 60 mV/decade, the threshold voltage,  $V_{th}$  that results in zero OFF-state subthreshold leakage current,  $I_{sub}$  (OFF), is about 140 mV. Increasing the subthreshold swing, S to 90 mV/decade increases the threshold

voltage,  $V_{th}$  for zero OFF-state subthreshold leakage current,  $I_{sub}$  (OFF) to about 180 mV. Further increment of the subthreshold swing, S to 120 mV/decade proportionally increases the threshold voltage,  $V_{th}$  for zero OFF-state subthreshold leakage current,  $I_{sub}$  (OFF) to about 240 mV.

Thus, for minimum leakage current, low values of the threshold voltage,  $V_{th} = 140$  mV and subthreshold swing, S of 60 mV/decade, are desirable.

From these observations, it can be concluded that, for given W and L, three options can be adopted as ways of minimizing  $I_{sub}$ . These include;

- i) Choosing a large  $V_{th}$ . This is, however, not desirable since a large  $V_{th}$  reduces the ON-current  $(I_{on})$  and therefore increases the gate delays.

- ii) Reducing the subthreshold swing, S by using a lower value of n. This can be achieved by increasing the gate oxide capacitance,  $C_{ox}$ , that is, by using a thinner gate oxide material, and decreasing the capacitance of the depletion layer,  $C_{dep}$ , the latter being achieved by increasing W.

- iii) Additionally, the transistor is operated at a lower temperature. Low operational temperature results in a low subthreshold slope factor, S as shown by equation (2.20). This last approach is valid in principle but rarely used because cooling adds considerable costs.

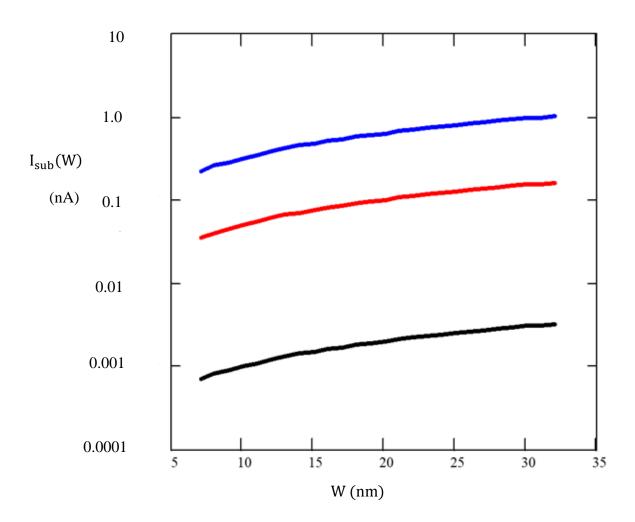

# 4.3 Effect of Channel width, W on the OFF-state subthreshold leakage current, $\mathbf{I}_{\text{sub}}$

The current through the device is measured for values of W ranging from 7 nm to 32 nm while the subthreshold swing, S in equation (3.14) is varied through S = 60, 90

and 120 mV/decade. The values of  $V_{th}$  and L are set at 300 mV and 10 nm respectively.

Substituting these values of S, L and  $V_{th}$  in the model equation (3.14) results in equations (4.2a), (4.2b) and (4.2c).

$$I_{sub1}(OFF)(A) = 100 \times \frac{W}{10} \times 10^{-9} \times 10^{\frac{-300}{60}}$$

(4.2a)

$$I_{sub2}(OFF)(A) = 100 \times \frac{W}{10} \times 10^{-9} \times 10^{\frac{-300}{90}}$$

(4.2b)

$$I_{sub3}(OFF)(A) = 100 \times \frac{W}{10} \times 10^{-9} \times 10^{\frac{-300}{120}}$$

(4.2c)

In the MATHCAD worksheet, the variable(s) and the function that depends on the behaviour of the variable are initially defined by entering,

$$W:7;32$$

(4.2d)

Equations (4.2a), (4.2b), (4.2c) and (4.2d) define the ranges of W and S over which  $I_{sub}(A)$  is passing through the device for different values of the subthreshold swing, S. The leakage current  $I_{sub}$  is a function of W, and it can be simplified from equations (4.2a), (4.2b) and (4.2c), together with the constant parameters in the model equation, and defined as,

$$I_{sub1}(W): 100 * \frac{W}{10} * 10^{-9} * 10^{\frac{-300}{60}}$$

(4.2e)

$$I_{sub2}(W): 100 * \frac{W}{10} * 10^{-9} * 10^{\frac{-300}{90}}$$

(4.2f)

$$I_{sub3}(W): 100 * \frac{W}{10} * 10^{-9} * 10^{\frac{-300}{120}}$$

(4.2g)

The data and its graphs were obtained by entering the commands,

W=

$$I_{sub1}(W) = I_{sub2}(W) = \text{and } I_{sub3}(W) =$$

(4.2h)

Figure 4.2 shows plots of the data obtained from equations (4.2e), (4.2f) and (4.2g) where the OFF-state subthreshold leakage current,  $I_{sub}$  is plotted against the device's channel width, W, for different values of the subthreshold swing, S.

Figure 4.2: Variation of Isub with W

The graphs show that the OFF-state subthreshold leakage current,  $I_{sub}$ , increases almost linearly with increase in the channel width, W, on first approximation. It can

also be seen that when the subthreshold swing, S=60 mV/decade, the OFF-state subthreshold leakage current,  $I_{sub}$  increases almost linearly from an approximate minimum of 1.0 pA to a maximum value of about 50 pA. When the subthreshold swing, S=90 mV/decade, the OFF-state subthreshold leakage current,  $I_{sub}$  increases almost linearly from an approximate minimum value of 500 pA to a maximum value of about 0.1 nA. When the subthreshold swing, S was further increased to 120 mV/decade, the OFF-state subthreshold leakage current,  $I_{sub}$  increased almost linearly from an approximate minimum value of 0.5 nA to a maximum value of about 1.0 nA.

Thus, for minimum leakage current, low values of W = 7 nm and the subthreshold swing, S of 60 mV/decade, are desirable.

The graphs also show that for a Silicon-based CMOS device, of minimum length, L= 10 nm and  $V_{gs}$  =0 (OFF-state), whose threshold voltage,  $V_{th}$  has been set at 300 mV and with a subthreshold swing, S of 60 mV/decade, the channel width, W, should be about 7 nm for minimal  $I_{sub}$ . ( $I_{sub} \approx 0.8 \text{ pA}$ ).

This is because if the channel width, W increases, the carrier density of the device also increases. This results in more carriers tunneling across the source-drain channel below the gate, hence increasing  $I_{sub}$ . The subthreshold swing, S indicates how much the gate voltage,  $V_{gs}$  must drop to decrease the leakage current by an order of magnitude. Thus, an increase in the subthreshold swing, S also causes an increase in the OFF-state subthreshold leakage current,  $I_{sub}$ .

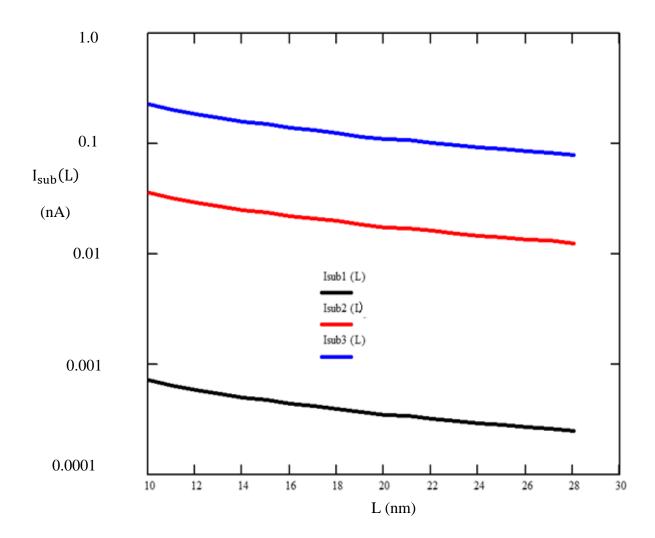

### 4.4 Effect of Channel length, L on the OFF-state subthreshold leakage current,

### $I_{sub}$

For the simulation process, the subthreshold swing, S is varied through three different values of S=60, 90 and 120 mV/decade. The current through the device is measured over this range of S, for the empirical value of  $V_{th}$  of 300 mV and L ranging from 10 nm to 28 nm, respectively.

Substituting these values of S, W and  $V_{th}$  in the model equation (3.14) results in equations (4.3a), (4.3b) and (4.3c),

$$I_{sub1}(OFF)(A) = 100 \times \frac{7}{L} \times 10^{-9} \times 10^{\frac{-300}{60}}$$

(4.3a)

$$I_{sub2}(OFF)(A) = 100 \times \frac{7}{L} \times 10^{-9} \times 10^{\frac{-300}{90}}$$

(4.3b)

$$I_{sub3}(OFF)(A) = 100 \times \frac{7}{L} \times 10^{-9} \times 10^{\frac{-300}{120}}$$

(4.3c)

In the MATHCAD worksheet, the variable(s) and the function that depends on the behaviour of the variable are initially defined by typing;

Equation (4.3d) defines the range of L over which  $I_{sub}(A)$  is passing through the device. The leakage current  $I_{sub}$  is a function of L, and it is simplified from equations (4.3a), (4.3b) and (4.3c), together with the constant parameters in the simulation equations, and defined as,

$$I_{sub1}(L): 100 * \frac{7}{L} * 10^{\circ} - 9 * 10^{\circ} \frac{-300}{60}$$

(4.3e)

$$I_{sub2}(L): 100 * \frac{7}{L} * 10^{\circ} - 9 * 10^{\circ} \frac{-300}{90}$$

(4.3f)

$$I_{sub3}(L): 100 * \frac{7}{L} * 10^{\circ} - 9 * 10^{\circ} \frac{-300}{120}$$

(4.3g)

The data and its graphs were obtained by entering the commands,

L=

$$I_{sub1}(L) = I_{sub2}(L) = \text{and } I_{sub3}(L) =$$

(4.3h)

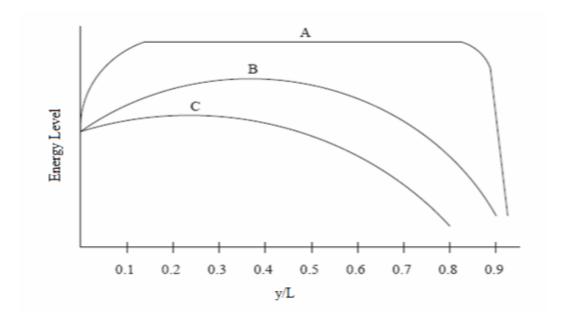

Figure 4.3 shows plots of the data obtained from equations (4.3e), (4.3f) and (4.3g) where the OFF-state subthreshold leakage current,  $I_{sub}$  is plotted against the channel length, L for the range of values of the subthreshold swing, S.

Figure 4.3: Variation of Isub with L.

The graphs show that the OFF-state subthreshold leakage current,  $I_{\text{sub}}$  (OFF) decreases almost linearly on first approximation with increase in the effective channel length, L of a Silicon-based CMOS transistor. The graphs also show that when the subthreshold swing, S=60 mV/decade, the OFF-state subthreshold leakage current,  $I_{sub}$  decreases almost linearly from an approximate maximum of 8.0 pA to a minimum value of about 5.0 pA. When the subthreshold swing, S=90 mV/decade, the OFF-state subthreshold leakage current,  $I_{sub}$  decreases almost linearly from an approximate maximum value of 50 pA to a minimum value of about 10 pA. When the subthreshold swing, S was further increased to 120 mV/decade, the OFF-state subthreshold leakage current,  $I_{sub}$  decreased almost linearly from an approximate maximum value of 0.5 nA to an approximate minimum value of about 0.1 nA. It can also be seen that, the OFF-state subthreshold leakage current,  $I_{sub}$  was much higher when S was raised to 90 and 120 mV/decade than when S was set at 60 mV/decade, shown by the wider gap between the former ranges of S and the latter.

Thus, for minimum leakage current, a high value of L= 28 nm and a low value of the subthreshold swing, S of 60 mV/decade, are desirable.

The graphs also show that for a Silicon-based CMOS device, of channel width, W= 7 nm and  $V_{gs}$  =0 (off-state), whose threshold voltage,  $V_{th}$  has been scaled to 300 mV and with a subthreshold swing, S of 60 mV/decade, the effective channel length should be about, L= 28 nm for minimal  $I_{sub}$ . ( $I_{sub} \approx 0.5 \ pA$ ).

### 4.5 Summary

The optimization of the OFF-state subthreshold leakage current in sub sections 4.2, 4.3 and 4.4, indicates that the values of L and W should be 20 nm and 7nm, respectively, while the threshold voltage should be scaled to  $V_{th}$ = 140 mV. The value of the subthreshold swing is 60 mV/decade.

Given that the subthreshold slope factor S is 60 mV/decade and the values of the transistor effective channel length, L is 28 nm, its channel width, W is 7 nm and the threshold voltage,  $V_{th}$  is 140 mV, then by equation (3.13), the value of the OFF-state subthreshold leakage current,  $I_{sub}$  (OFF) for a single CMOS device will be,

$$I_{sub}(OFF)(A) = 100 \times \frac{7}{28} \times 10^{-9} \times 10^{\frac{-140}{60}}$$

(4.4)

$$I_{sub}(OFF)(A) = 1.25 \times 10^{-10} A$$

$$I_{sub}(OFF)(nA) = 0.125 \, nA$$

(4.5)